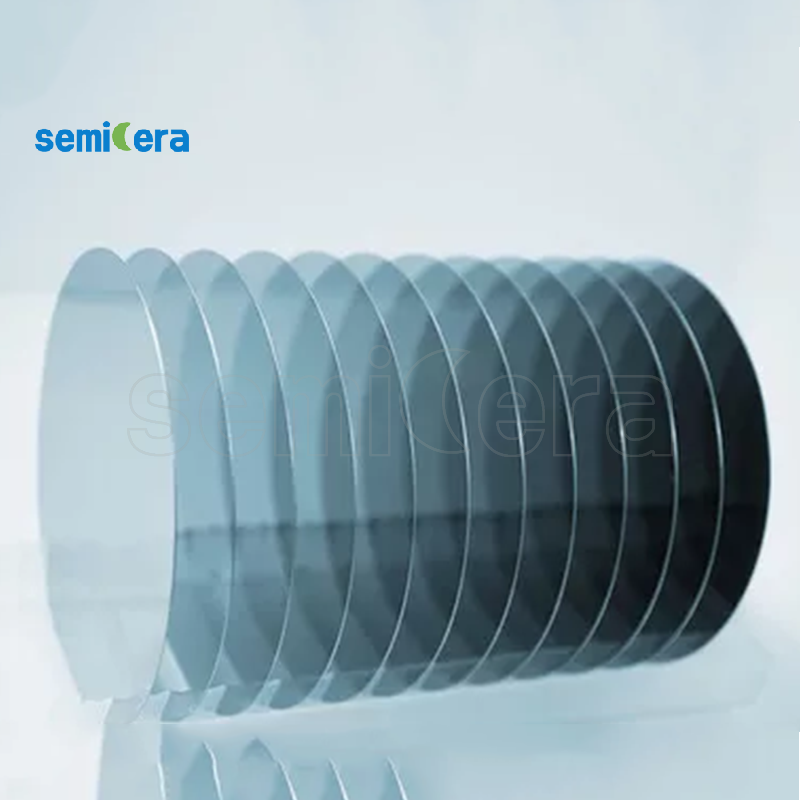

세미세라고품질을 소개합니다Si 에피택시오늘날 반도체 산업의 엄격한 표준을 충족하도록 설계된 서비스입니다. 에피택시 실리콘 레이어는 전자 장치의 성능과 신뢰성에 매우 중요하며 당사의 Si 에피택시 솔루션은 구성 요소가 최적의 기능을 달성하도록 보장합니다.

정밀 성장 실리콘 레이어 세미세라는 고성능 기기의 기본은 사용된 재료의 품질에 달려 있음을 이해합니다. 우리의Si 에피택시프로세스는 탁월한 균일성과 결정 무결성을 갖춘 실리콘 층을 생성하기 위해 꼼꼼하게 제어됩니다. 이러한 레이어는 일관성과 신뢰성이 가장 중요한 마이크로 전자공학부터 고급 전력 장치까지 다양한 응용 분야에 필수적입니다.

장치 성능에 최적화됨그만큼Si 에피택시Semicera가 제공하는 서비스는 장치의 전기적 특성을 향상시키기 위해 맞춤화되었습니다. 결함 밀도가 낮은 고순도 실리콘 층을 성장시킴으로써 캐리어 이동성이 향상되고 전기 저항이 최소화되어 부품이 최상의 성능을 발휘하도록 보장합니다. 이러한 최적화는 현대 기술이 요구하는 고속 및 고효율 특성을 달성하는 데 중요합니다.

응용 분야의 다양성 세미세라'에스Si 에피택시CMOS 트랜지스터, 파워 MOSFET, 바이폴라 접합 트랜지스터 생산을 포함한 광범위한 애플리케이션에 적합합니다. 당사의 유연한 프로세스를 통해 고주파 응용 분야에 얇은 레이어가 필요한지, 전력 장치에 더 두꺼운 레이어가 필요한지 여부에 관계없이 프로젝트의 특정 요구 사항에 따라 맞춤화가 가능합니다.

우수한 재료 품질품질은 Semicera에서 하는 모든 일의 핵심입니다. 우리의Si 에피택시이 공정은 최첨단 장비와 기술을 사용하여 각 실리콘 층이 최고 수준의 순도와 구조적 무결성을 충족하는지 확인합니다. 세부 사항에 대한 이러한 관심은 장치 성능에 영향을 미칠 수 있는 결함 발생을 최소화하여 더 안정적이고 오래 지속되는 구성 요소를 만듭니다.

혁신에 대한 헌신 세미세라반도체 기술의 선두에 서기 위해 최선을 다하고 있습니다. 우리의Si 에피택시서비스는 에피택셜 성장 기술의 최신 발전을 통합하여 이러한 약속을 반영합니다. 우리는 업계의 변화하는 요구 사항을 충족하는 실리콘 레이어를 제공하기 위해 프로세스를 지속적으로 개선하여 귀하의 제품이 시장에서 경쟁력을 유지할 수 있도록 보장합니다.

귀하의 요구에 맞는 맞춤형 솔루션모든 프로젝트가 독특하다는 것을 이해하고,세미세라맞춤형 제안Si 에피택시귀하의 특정 요구 사항에 맞는 솔루션을 제공합니다. 특정 도핑 프로파일, 층 두께 또는 표면 마감이 필요한 경우 당사 팀은 귀하와 긴밀히 협력하여 귀하의 정확한 사양을 충족하는 제품을 제공합니다.

| 품목 | 생산 | 연구 | 더미 |

| 크리스탈 매개변수 | |||

| 폴리타입 | 4H | ||

| 표면 방향 오류 | <11-20 >4±0.15° | ||

| 전기적 매개변수 | |||

| 도펀트 | n형 질소 | ||

| 비저항 | 0.015-0.025ohm·cm | ||

| 기계적 매개변수 | |||

| 지름 | 150.0±0.2mm | ||

| 두께 | 350±25μm | ||

| 기본 평면 방향 | [1-100]±5° | ||

| 기본 플랫 길이 | 47.5±1.5mm | ||

| 2차 아파트 | 없음 | ||

| TTV | 5μm 이하 | 10μm 이하 | 15μm 이하 |

| LTV | ≤3μm(5mm*5mm) | ≤5μm(5mm*5mm) | 10μm 이하(5mm*5mm) |

| 절하다 | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| 경사 | ≤35μm | 45μm 이하 | ≤55μm |

| 전면(Si-face) 거칠기(AFM) | Ra≤0.2nm(5μm*5μm) | ||

| 구조 | |||

| 마이크로파이프 밀도 | <1개/cm2 | <10개/cm2 | <15개/cm2 |

| 금속 불순물 | ≤5E10원자/cm2 | NA | |

| BPD | ≤1500개/cm2 | ≤3000개/cm2 | NA |

| 티에스디 | ≤500개/cm2 | ≤1000개/cm2 | NA |

| 전면 품질 | |||

| 앞쪽 | Si | ||

| 표면 마무리 | Si-페이스 CMP | ||

| 입자 | ≤60개/웨이퍼(크기≥0.3μm) | NA | |

| 긁힌 자국 | ≤5ea/mm. 누적 길이 ≤직경 | 누적 길이≤2*직경 | NA |

| 오렌지 껍질/구덩이/얼룩/줄무늬/균열/오염 | 없음 | NA | |

| 가장자리 칩/압흔/파손/육각 플레이트 | 없음 | ||

| 다형 영역 | 없음 | 누적 면적 ≤20% | 누적 면적 ≤30% |

| 전면 레이저 마킹 | 없음 | ||

| 뒷면 품질 | |||

| 백마무리 | C-페이스 CMP | ||

| 긁힌 자국 | ≤5ea/mm, 누적 길이≤2*직경 | NA | |

| 뒷면 결함(가장자리 칩/압흔) | 없음 | ||

| 뒷면 거칠기 | Ra≤0.2nm(5μm*5μm) | ||

| 후면 레이저 마킹 | 1mm(상단 가장자리부터) | ||

| 가장자리 | |||

| 가장자리 | 모따기 | ||

| 포장 | |||

| 포장 | 진공 포장으로 Epi 준비 완료 다중 웨이퍼 카세트 포장 | ||

| *참고: "NA"는 요청 없음을 의미합니다. 언급되지 않은 항목은 SEMI-STD를 참조할 수 있습니다. | |||