1.집적회로에 대하여

1.1 집적회로의 개념과 탄생

집적회로(IC): 일련의 특정 처리 기술을 통해 트랜지스터, 다이오드 등의 능동 소자와 저항기, 커패시터 등의 수동 소자를 결합한 장치를 말합니다.

특정 회로 상호 연결에 따라 반도체(예: 실리콘 또는 갈륨 비소와 같은 화합물) 웨이퍼에 "통합"된 다음 특정 기능을 수행하기 위해 쉘에 패키징되는 회로 또는 시스템입니다.

1958년 TI(Texas Instruments)에서 전자 장비 소형화를 담당했던 Jack Kilby는 집적 회로에 대한 아이디어를 제안했습니다.

“커패시터, 저항기, 트랜지스터 등 모든 부품을 하나의 재료로 만들 수 있기 때문에 이를 반도체 재료 위에 만든 뒤 상호 연결해 완전한 회로를 구성하는 것이 가능하리라 생각했습니다.”

1958년 9월 12일과 9월 19일에 Kilby는 각각 위상 변이 발진기와 트리거의 제조와 시연을 완료하여 집적 회로의 탄생을 알렸습니다.

2000년에 킬비는 노벨 물리학상을 수상했습니다. 노벨상 위원회는 킬비가 "현대 정보 기술의 토대를 마련했다"고 말한 적이 있습니다.

아래 그림은 Kilby와 그의 집적 회로 특허를 보여줍니다.

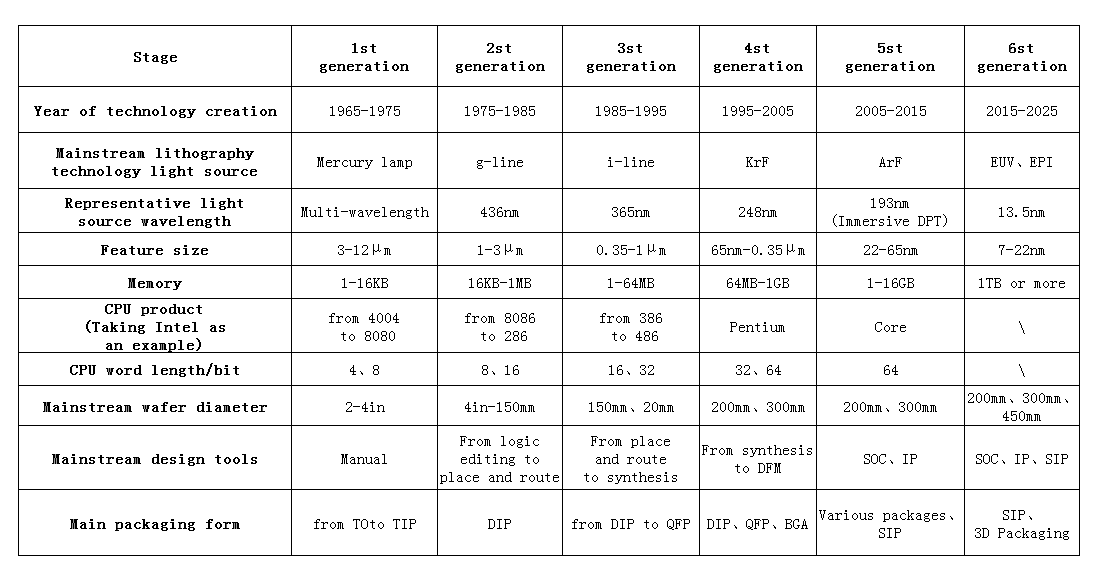

1.2 반도체 제조기술의 발전

다음 그림은 반도체 제조 기술의 발전 단계를 보여줍니다.

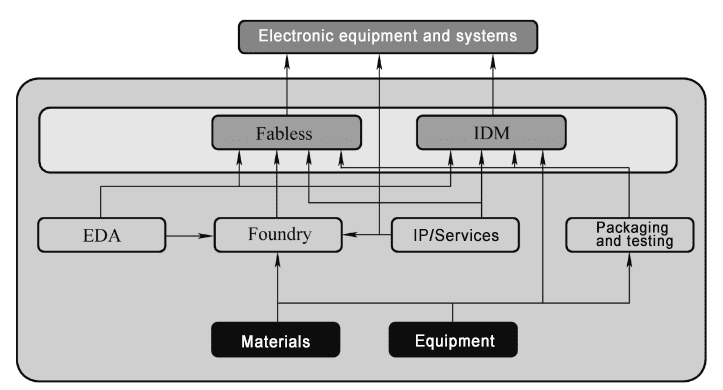

1.3 집적 회로 산업 체인

반도체 산업 체인(주로 개별 장치를 포함한 집적 회로)의 구성은 위 그림에 나와 있습니다.

- 팹리스(Fabless): 생산라인 없이 제품을 디자인하는 회사.

- IDM: 통합 장치 제조업체, 통합 장치 제조업체;

- IP: 회로 모듈 제조업체;

- EDA: 전자 설계 자동, 전자 설계 자동화, 회사는 주로 설계 도구를 제공합니다.

- 주조소; 칩 제조 서비스를 제공하는 웨이퍼 파운드리

- 패키징 및 테스트 파운드리 회사: 주로 Fabless 및 IDM에 서비스를 제공합니다.

- 소재 및 특수장비업체 : 주로 칩제조업체에 필요한 소재 및 장비를 제공합니다.

반도체 기술을 사용하여 생산되는 주요 제품은 집적 회로와 개별 반도체 장치입니다.

집적 회로의 주요 제품은 다음과 같습니다.

- ASSP(응용프로그램별 표준 부품);

- 마이크로프로세서 유닛(MPU);

- 메모리

- ASIC(주문형 집적 회로);

- 아날로그 회로;

- 일반논리회로(Logical Circuit).

반도체 디스크리트 디바이스의 주요 제품은 다음과 같습니다.:

- 다이오드;

- 트랜지스터;

- 전원 장치;

- 고전압 장치;

- 전자레인지 장치;

- 광전자공학;

- 센서 장치(센서).

2. 집적회로 제조공정

2.1 칩 제조

수십 또는 수만 개의 특정 칩을 실리콘 웨이퍼에서 동시에 만들 수 있습니다. 실리콘 웨이퍼에 들어가는 칩의 개수는 제품의 종류와 각 칩의 크기에 따라 달라집니다.

실리콘 웨이퍼는 일반적으로 기판이라고 불립니다. 실리콘 웨이퍼의 직경은 초기 1인치 미만에서 현재 일반적으로 사용되는 12인치(약 300mm)까지 해를 거듭하며 증가해 왔으며, 14인치 또는 15인치로 전환되고 있다.

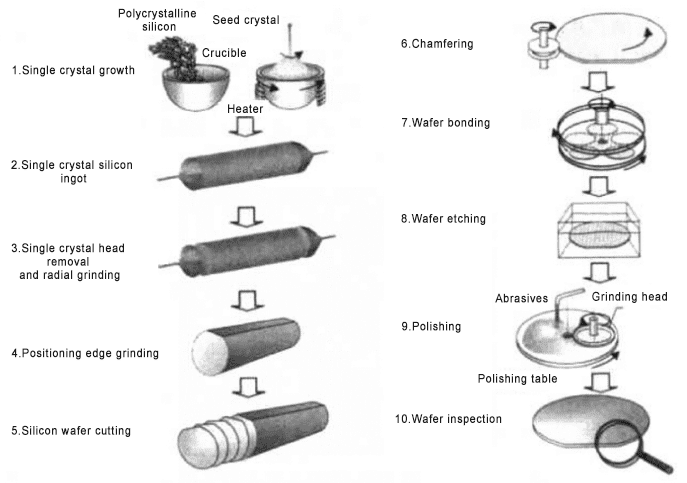

칩 제조는 일반적으로 실리콘 웨이퍼 준비, 실리콘 웨이퍼 제조, 칩 테스트/피킹, 조립 및 패키징, 최종 테스트의 5단계로 구분됩니다.

(1)

실리콘 웨이퍼 준비:

원료를 만들기 위해 모래에서 실리콘을 추출하고 정제합니다. 특별한 공정을 통해 적절한 직경의 실리콘 잉곳이 생산됩니다. 잉곳은 마이크로칩을 만들기 위해 얇은 실리콘 웨이퍼로 절단됩니다.

웨이퍼는 등록 가장자리 요구 사항 및 오염 수준과 같은 특정 사양에 맞게 준비됩니다.

(2)실리콘 웨이퍼 제조:

칩 제조라고도 알려진 베어 실리콘 웨이퍼는 실리콘 웨이퍼 제조 공장에 도착한 후 다양한 세척, 필름 형성, 포토리소그래피, 에칭 및 도핑 단계를 거칩니다. 처리된 실리콘 웨이퍼에는 실리콘 웨이퍼에 영구적으로 에칭된 완전한 집적 회로 세트가 있습니다.

(3)실리콘 웨이퍼 테스트 및 선택:

실리콘 웨이퍼 제조가 완료된 후 실리콘 웨이퍼는 테스트/분류 영역으로 보내져 개별 칩을 조사하고 전기적으로 테스트합니다. 그런 다음 허용 가능한 칩과 허용되지 않는 칩을 분류하고 결함이 있는 칩을 표시합니다.

(4)조립 및 포장:

웨이퍼 테스트/분류 후 웨이퍼는 조립 및 패키징 단계에 들어가 개별 칩을 보호 튜브 패키지에 포장합니다. 기판의 두께를 줄이기 위해 웨이퍼 뒷면을 연삭합니다.

각 웨이퍼 뒷면에 두꺼운 플라스틱 필름을 부착한 후 다이아몬드 팁 톱날을 사용하여 앞면의 스크라이브 라인을 따라 각 웨이퍼의 칩을 분리합니다.

실리콘 웨이퍼 뒷면의 플라스틱 필름은 실리콘 칩이 떨어지는 것을 방지합니다. 조립 공장에서는 양호한 칩을 압축하거나 배출하여 조립 패키지를 형성합니다. 나중에 칩은 플라스틱이나 세라믹 껍질에 밀봉됩니다.

(5)최종 테스트:

칩의 기능을 보장하기 위해 각 패키지 집적 회로는 제조업체의 전기 및 환경 특성 매개변수 요구 사항을 충족하는지 테스트됩니다. 최종 테스트 후 칩은 전용 위치에서 조립할 수 있도록 고객에게 전송됩니다.

2.2 공정 구분

집적 회로 제조 공정은 일반적으로 다음과 같이 나뉩니다.

프런트엔드: 프론트엔드 공정은 일반적으로 트랜지스터 등의 소자 제조 공정을 말하며, 주로 소자 분리, 게이트 구조, 소스 및 드레인, 콘택홀 등의 형성 공정을 포함합니다.

백엔드: 백엔드 공정은 주로 칩 위의 다양한 소자에 전기적 신호를 전달할 수 있는 배선을 형성하는 공정을 말하며, 주로 배선 사이의 유전증착, 메탈라인 형성, 리드패드 형성 등의 공정을 포함한다.

중간 단계: 트랜지스터의 성능 향상을 위해 45nm/28nm 이후의 첨단 기술 노드에서는 High-k 게이트 유전체와 금속 게이트 공정을 사용하고, 트랜지스터 소스 및 드레인 구조를 준비한 후 교체 게이트 공정과 로컬 상호 연결 공정을 추가합니다. 이러한 프로세스는 프런트엔드 프로세스와 백엔드 프로세스 사이에 있으며 기존 프로세스에서는 사용되지 않으므로 중간 단계 프로세스라고 합니다.

일반적으로 콘택홀 준비 공정은 전공정과 후공정을 나누는 경계선이다.

콘택트홀: 1층 금속 배선과 기판 소자를 연결하기 위해 실리콘 웨이퍼에 수직으로 식각된 구멍. 텅스텐 등의 금속을 채워 소자전극을 금속배선층으로 연결하는 역할을 한다.

스루홀: 금속 배선의 인접한 두 층 사이의 연결 경로로 두 금속층 사이의 유전층에 위치하며 일반적으로 구리와 같은 금속으로 채워져 있습니다.

넓은 의미에서:

프론트엔드 프로세스: 넓은 의미에서 집적 회로 제조에는 테스트, 패키징 및 기타 단계도 포함되어야 합니다. 테스트 및 패키징과 비교할 때 구성 요소 및 상호 연결 제조는 집적 회로 제조의 첫 번째 부분으로 통칭하여 프런트엔드 프로세스라고 합니다.

백엔드 프로세스: 테스트 및 패키징을 백엔드 프로세스라고 합니다.

3. 부록

SMIF:표준 기계 인터페이스

AMHS:자동 자재 취급 시스템

OHT : 오버헤드 호이스트 트랜스퍼

FOUP: 전면 개방형 통합 포드, 12인치(300mm) 웨이퍼 전용

더 중요한 것은,Semicera가 제공할 수 있는흑연 부품, 부드러움/경질 펠트,실리콘 카바이드 부품, CVD 탄화규소 부품, 그리고SiC/TaC 코팅 부품30일 안에 전체 반도체 공정을 완료할 수 있습니다.우리는 중국에서 귀하의 장기적인 파트너가 되기를 진심으로 기대합니다.

게시 시간: 2024년 8월 15일