반도체 공정 개요

반도체 공정에는 주로 기판, 프레임 등 다양한 영역 내에서 칩과 기타 요소를 완전히 연결하기 위해 미세 가공 및 필름 기술을 적용하는 작업이 포함됩니다. 이를 통해 리드 단자 추출과 플라스틱 절연 매체로 캡슐화하여 통합된 전체를 형성하고 3차원 구조로 표현되어 궁극적으로 반도체 패키징 공정이 완성됩니다. 반도체 공정의 개념은 반도체 칩 패키징의 좁은 정의와도 관련이 있습니다. 더 넓은 관점에서 보면 기판에 연결 및 고정하고, 해당 전자 장비를 구성하고, 강력하고 포괄적인 성능을 갖춘 완전한 시스템을 구축하는 패키징 엔지니어링을 의미합니다.

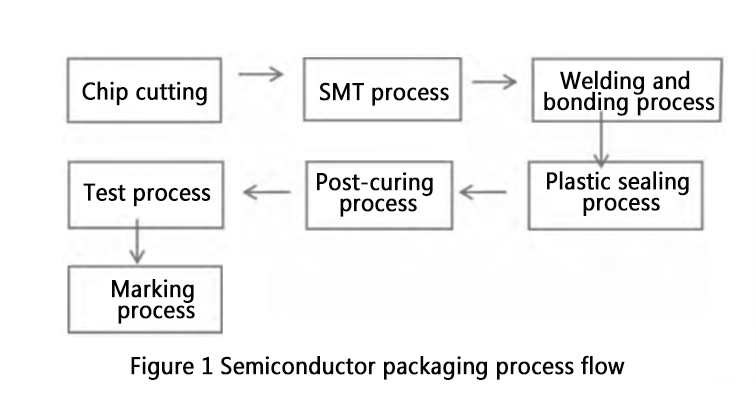

반도체 패키징 공정 흐름

그림 1에 표시된 것처럼 반도체 패키징 프로세스에는 여러 작업이 포함됩니다. 각 프로세스에는 특정 요구 사항과 밀접하게 관련된 작업 흐름이 있으므로 실제 단계에서 자세한 분석이 필요합니다. 구체적인 내용은 다음과 같습니다.

1. 칩 커팅

반도체 패키징 공정에서 칩커팅(Chip Cutting)은 실리콘 웨이퍼를 개별 칩으로 썰고, 실리콘 찌꺼기를 신속히 제거해 후속 작업과 품질관리에 지장을 주지 않는 작업이다.

2. 칩 마운팅

칩 마운팅 공정은 보호 필름층을 적용해 웨이퍼 연삭 중 회로 손상을 방지하는 데 중점을 두고 회로 무결성을 지속적으로 강조합니다.

3. 와이어 본딩 공정

와이어 본딩 프로세스의 품질 제어에는 다양한 유형의 금 와이어를 사용하여 칩의 본딩 패드를 프레임 패드와 연결하고, 칩이 외부 회로에 연결될 수 있도록 하고 전반적인 프로세스 무결성을 유지하는 작업이 포함됩니다. 일반적으로 도핑된 금 와이어와 합금된 금 와이어가 사용됩니다.

도핑된 금 와이어: 유형에는 GS, GW 및 TS가 포함되며 높은 아크(GS: >250μm), 중간 높은 아크(GW: 200~300μm) 및 중간 낮은 아크(TS: 100~200)에 적합합니다. μm) 각각 결합.

합금 금 와이어: 유형에는 AG2 및 AG3이 포함되며 낮은 아크 본딩(70-100μm)에 적합합니다.

이 와이어의 직경 옵션은 0.013mm ~ 0.070mm입니다. 운영 요구 사항 및 표준에 따라 적절한 유형과 직경을 선택하는 것은 품질 관리에 매우 중요합니다.

4. 성형공정

몰딩 요소의 주요 회로에는 캡슐화가 포함됩니다. 성형 공정의 품질을 제어하면 특히 다양한 정도의 손상을 유발하는 외부 힘으로부터 부품을 보호할 수 있습니다. 여기에는 구성 요소의 물리적 특성에 대한 철저한 분석이 포함됩니다.

현재 세 가지 주요 방법이 사용됩니다: 세라믹 포장, 플라스틱 포장, 전통 포장. 글로벌 칩 생산 수요를 충족하려면 각 패키징 유형의 비율을 관리하는 것이 중요합니다. 이 과정에서는 칩과 리드프레임을 에폭시 수지로 봉지하기 전 예열, 몰딩, 몰드 후 경화 등 종합적인 능력이 필요합니다.

5. 후경화 공정

성형 공정 후에는 공정이나 패키지 주변의 잉여 물질을 제거하는 데 중점을 둔 후경화 처리가 필요합니다. 전반적인 공정 품질과 외관에 영향을 주지 않으려면 품질 관리가 필수적입니다.

6. 테스트 프로세스

이전 프로세스가 완료되면 고급 테스트 기술과 시설을 사용하여 프로세스의 전반적인 품질을 테스트해야 합니다. 이 단계에서는 성능 수준에 따라 칩이 정상적으로 작동하는지 여부에 초점을 맞춰 데이터를 자세히 기록합니다. 테스트 장비 비용이 높기 때문에 육안 검사 및 전기 성능 테스트를 포함하여 생산 단계 전반에 걸쳐 품질 관리를 유지하는 것이 중요합니다.

전기 성능 테스트: 여기에는 자동 테스트 장비를 사용하여 집적 회로를 테스트하고 각 회로가 전기 테스트를 위해 올바르게 연결되었는지 확인하는 작업이 포함됩니다.

육안 검사: 기술자는 현미경을 사용하여 완성된 패키지 칩을 철저하게 검사하여 결함이 없고 반도체 패키징 품질 표준을 충족하는지 확인합니다.

7. 마킹 과정

마킹 프로세스에는 최종 처리, 품질 검사, 포장 및 배송을 위해 테스트된 칩을 반제품 창고로 옮기는 작업이 포함됩니다. 이 프로세스에는 세 가지 주요 단계가 포함됩니다.

1)전기도금 : 리드를 형성한 후 부식방지재를 도포하여 산화 및 부식을 방지합니다. 대부분의 리드가 주석으로 만들어지기 때문에 전기 도금 증착 기술이 일반적으로 사용됩니다.

2) 굽힘: 처리된 리드는 리드 형성 도구에 배치된 집적 회로 스트립을 사용하여 리드 모양(J 또는 L 유형) 및 표면 실장 패키징을 제어하여 모양을 만듭니다.

3) 레이저 프린팅(Laser Printing) : 마지막으로 성형된 제품에 그림 3과 같이 반도체 패키징 공정의 특수 마크 역할을 하는 디자인을 인쇄한다.

과제 및 권장 사항

반도체 패키징 공정에 대한 연구는 반도체 기술의 개요를 이해하고 그 원리를 이해하는 것에서부터 시작됩니다. 다음으로, 포장 프로세스 흐름을 검토하는 것은 일상적인 문제를 방지하기 위해 세련된 관리를 사용하여 작업 중 세심한 제어를 보장하는 것을 목표로 합니다. 현대 개발의 맥락에서 반도체 패키징 공정의 과제를 식별하는 것은 필수적입니다. 프로세스 품질을 효과적으로 향상시키기 위해서는 품질 관리 측면에 중점을 두고 핵심 사항을 철저히 숙지하는 것이 좋습니다.

품질 관리 관점에서 분석해 보면, 각각 서로 영향을 미치는 특정 콘텐츠와 요구 사항이 있는 수많은 프로세스로 인해 구현 중에 상당한 어려움이 있습니다. 실제 작업 중에는 엄격한 제어가 필요합니다. 세심한 작업 태도와 첨단 기술 적용을 통해 반도체 패키징 공정 품질과 기술 수준을 향상시켜 종합적인 적용 효율성을 보장하고 우수한 종합적 이점을 얻을 수 있습니다(그림 3 참조).

게시 시간: 2024년 5월 22일